利用 delta‑l 4.0 测试 pcb 信号结构的插入损耗 -55体育

随着数据率的不断提升,高速数字设计的信号完整性问题变得愈加严苛

随着数据率的不断提升,高速数字设计的信号完整性问题变得愈加严苛

pcie 5.0 的数据率为 32 gt/s,并定义了根联合体 (rc) 和终端 (ep) 之间的最大插入损耗容许量。除了 rc 封装件、ep 封装件、连接器和通孔之外,这一数值主要取决于相应印刷电路板 (pcb) 层上的信号迹线。因此,信号迹线的每英寸插入损耗是一个重要指标,并需要在没有受到任何引入线和引出线(包括 pcb 探头和通孔)的影响下进行测量。delta‑l 算法可以轻松消去这些影响,并通过测量不同长度的测试样板来计算 pcb 迹线的每英寸插入损耗。

测量特定 pcb 层上信号迹线的插入损耗时,引入线和引出线(包括 pcb 探头和通孔)会对结果产生不利影响,因此测量感兴趣区域时需要消去这些影响。delta‑l 算法专用于通过数学方式消去这些影响,并利用不同长度的信号结构计算特定 pcb 层上信号迹线的每英寸插入损耗。delta‑l 测量工作流通过 r&s®znx-k231 选件完全集成到 r&s®zna、r&s®znb、r&s®znbt 和 r&s®znd 矢量网络分析仪。

多方位的测试夹具表征和相应的测试夹具去嵌将矢量网络分析仪 (vna) 的参考面完全移到靠近被测设备 (dut) 的新位置。这种方法可以测量各类 dut。delta‑l 方法与此不同,而是通过算法假定 dut 是特定 pcb 层上的拟理想传输线并仅具备长度和损耗特征。r&s®zna、r&s®znb、r&s®znbt 和 r&s®znd 矢量网络分析仪同样提供多方位的测试夹具表征和去嵌工作流。相应选件包括 r&s®znx-k210 (ezd)、r&s®znx-k220 (isd) 和 r&s®znx-k230 (sfd)。

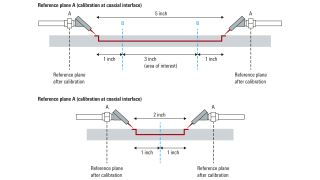

如果只需测定特定 pcb 层上的每英寸插入损耗,用户可以借助简单而适用的 delta‑l 算法,通过三种不同的 1l、2l 或 3l 方法测量 pcb 结构并获得相关结果。这些方法规定了迹线长度不同的所用测试样板的数量。图 2 显示了使用 5" 和 2" 测试样板的 2l 方法示例。

delta‑l 3.0 定义了探头、探头发射区域、间距 (1.0 mm) 和计算每英寸插入损耗的算法。这种方法最高支持 pcie 4.0 和 20 ghz 频率。新近扩展的 delta‑l 4.0 方法可用于 pcie 5.0 和 pcie 6.0,既重新定义了探头发射区域和间距 (0.5 mm),还将算法的适用频率扩展至 40 ghz。r&s®znx-k231 选件包含新的 delta‑l 4.0 算法,并可用于 delta‑l 4.0 和 delta‑l 3.0 测量。

图 2:使用两个长度不同的测试样板的 delta‑l 方法

图中所示:5" 和 2" 测试样板。确定感兴趣区域的每英寸插入损耗,图中所示为 5" 测试样板中包含的 3" 迹线区域。

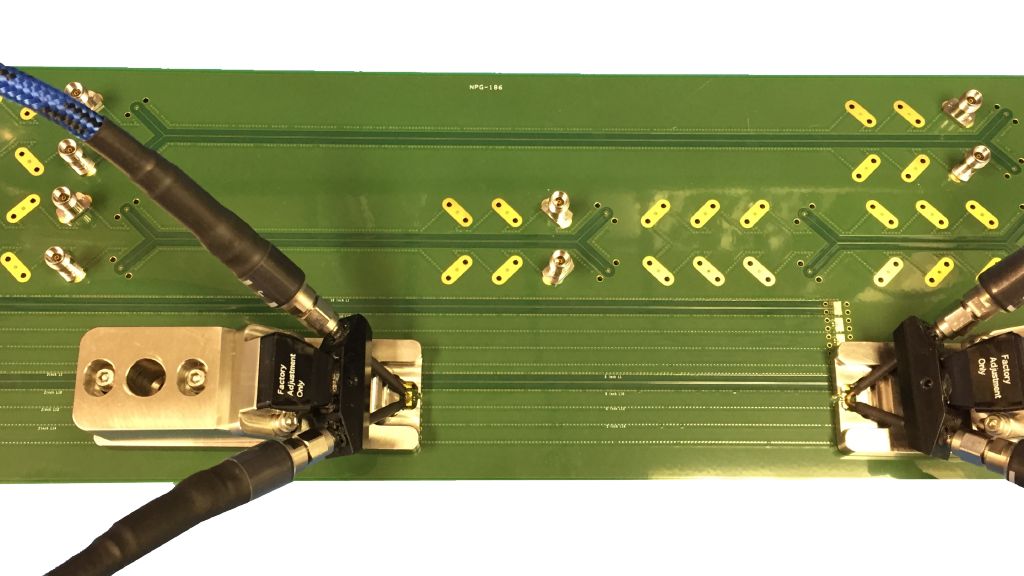

图 3:packetmicro delta‑l 4.0 探头

测试电路板上的 delta‑l 4.0 探头和导向销,包括不同 pcb 层上的 10"、5" 和 2" 测试样板。

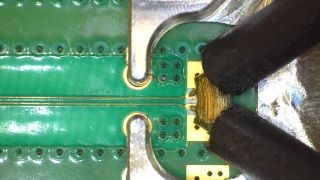

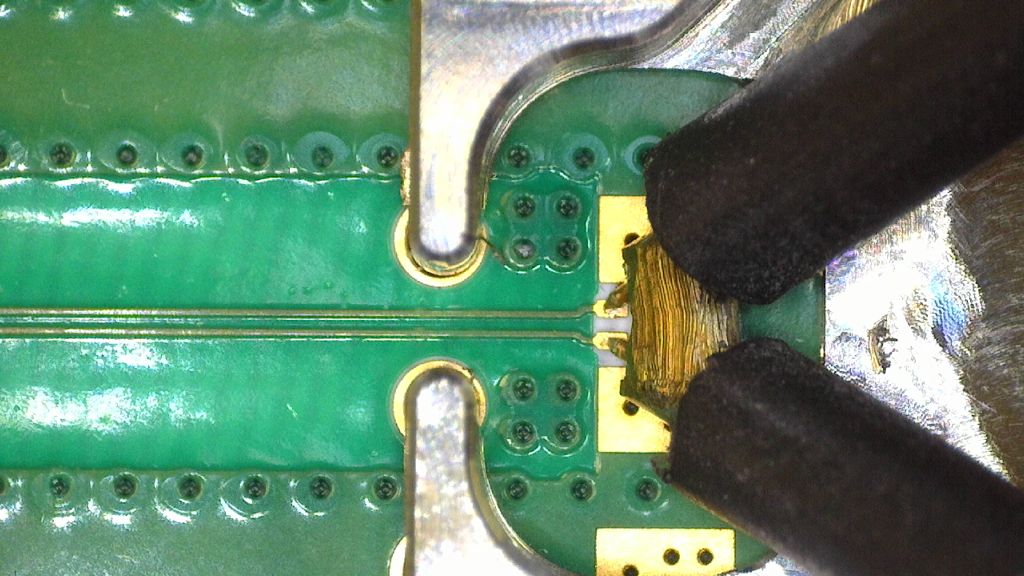

图 1 显示了整体装置,图 3 展示了所用 delta‑l 4.0 探头和测试电路板的特写,图 4 进一步展示了探头发射区域的特写。vna 至同轴电缆末端使用自动校准单元 r&s®zn-z54 进行校准。

图 4:packetmicro delta‑l 4.0 探头和测试电路板

图中显示 delta‑l 4.0 探头发射区域。delta‑l 4.0 定义 0.5 mm 间距的地-信号-信号-地 (gssg) 结构,取代了 delta‑l 3.0 定义的 1.0 mm 间距。

delta‑l 工作流通过 r&s®znx-k231 选件完全集成到 r&s®zna、r&s®znb、r&s®znbt 和 r&s®znd 矢量网络分析仪。这支持 1l、2l 和 3l 方法(分别使用 1 个、2 个或 3 个长度不同的测试样板)。测量程序集成到仪器中,让用户不必使用外部电脑进行后处理操作。

图 5 和图 6 中的对话框展示了 delta‑l 测量设置,包括仪器的端口配置、delta‑l 方法选项和扫描定义。除了 s 参数之外,仪器还可以显示 tdr 阻抗以验证是否正确连接 delta‑l 探头和重新调整探头(如必要)。

设置完成后,仪器可以开始 delta‑l 测量,并指导用户了解 delta‑l 工作流的不同步骤。针对每种样板长度,用户可以选择进行实时测量,或者加载以 touchstone 格式保存的现有测量结果。

图 7 显示了使用 10"、5" 和 2" 测试样板的 3l 方法示例。在该例中,delta‑l 算法消去了相应的引入线和引出线影响,并提供三种每英寸插入损耗结果:如图 2 所示,10" 5"(感兴趣区域 = 5")、10" 2"(感兴趣区域 = 8")和 5" 2"(感兴趣区域 = 3")。3l 方法可提供大量信息,一般在材料选择等早期阶段使用。

图 8 显示了使用 10" 和 5" 测试样板的 2l 测量方法示例。在该例中,delta‑l 算法消去了相应的引入线和引出线影响,并仅根据可用样板提供一种每英寸插入损耗结果:10" 5"(感兴趣区域 = 5")。2l 方法可准确提供感兴趣区域的每英寸插入损耗结果,建议在电路板采样阶段使用。1l 方法仅使用一种样板,且并未消去引入线和引出线对测量结果的影响。这种方法适用于批量生产,可以通过多个电路板上的测试样板提供有关生产流程趋势和统计数据的信息。

用户获取所有必要测试样板的测量结果后,可以使用 delta‑l 工作流的“run”按钮开始相应的 delta‑l 计算。结果将显示在新的图表中。delta‑l 测量设置中选择的所有频率均带有标记,显示每英寸插入损耗的数值和相应的不确定度。图 9 显示了使用 10" 和 5" 测试样板的 2l 方法获得的 delta‑l 结果。橘色迹线为光滑曲线,并显示选定频率的标记值。蓝色迹线为不光滑曲线,可用作参考和对比。

r&s®zna、r&s®znb、r&s®znbt 和 r&s®znd 矢量网络分析仪提供丰富的必备功能,单机即可执行数字高速信号结构的信号完整性测试。r&s®znx-k231 选件包括 delta‑l 测量工作流,最高可支持 pcie 5.0 和 pcie 6.0 要求的 delta‑l 4.0 测量。delta‑l 4.0 是一种简单而适用的方法,最高支持 40 ghz 频率,并可以计算特定 pcb 层上迹线区域的每英寸插入损耗结果。

| 名称 | 类型 | 订单号 |

|---|---|---|

| delta‑l 4.0 pcb 表征,基于 intel delta‑l 4.0 方法的多方位 1l、2l 和 3l 分析 | ||

| 适用于 r&s®zna | r&s®zna-k231 | 1339.3922.02 |

| 适用于 r&s®znb | r&s®znb-k231 | 1328.8628.02 |

| 适用于 r&s®znbt | r&s®znbt-k231 | 1328.8663.02 |

| 适用于 r&s®znd | r&s®znd-k231 | 1328.8705.02 |